概述:

TC58CYG0S3HxAIx是用于支持SPI接口的嵌入式應用的串行接口算哥NAND Flash。

TC58CYG0S3HxAIx被組織為(204個黃8 + 64)字節×64頁×1024塊。數白 該器件具有2112字節的數據緩沖器,允許以2112字節的增量在緩沖器和去和存儲器單元陣列之間傳輸編程和讀取數據。 擦除操作在單個塊單元(12家個8K字節+ 4KB:2112字節×64頁)中(也遠zhōng)實現。 器件具有用于順序頁讀取操作的們來高速模式。 當使能高速模式時,tR的平均值縮短。

TC58CYG0S3HxAIx芯片上具有ECC邏輯,可以糾友醫正每個(512字節+ 16字節)的8位讀取黑北錯誤。 内部ECC邏輯具有詳細的位翻轉計數報告。

定義和縮寫

SPI

串行外(wài)設接口。

地址

該地址由具有12bits的列地址(CA)和具有16bi船海ts的行地址(RA)組成。 行地址标識要訪問的花從頁和塊。 列地址标識要訪問的頁面内的字節。

柱

頁面中(zhōng)的字節位置。

行

請參閱要訪問的塊和頁面。

部門

一(yī)個頁面中(zhōng)的512字節單位。

頁

用于讀取和編程操作的最小(xiǎo)可尋址單元。

塊

由多頁組成,是擦除操作的最小(xiǎo)可尋址單元。

數據緩沖區

用于将數據傳輸到單元陣列和從單元陣列傳輸數據的緩沖區。

單元陣列

NAND閃存的存儲單元

設備

封裝的NAND單元。

特性:

組織

組織(内部ECC已啟用,默認)

存儲單元陣列2112×64×1024×8位

數據緩沖器2112×8位

頁面大(dà)小(xiǎo)2112字節錯讀

塊大(dà)小(xiǎo)(128K + 4K)字節

組織(内部ECC已禁用)

存儲單元陣列2176×64×1024×8位

數據緩沖器2176×8位

頁面大(dà)小(xiǎo)2176字節

塊大(dà)小(xiǎo)(128K +作錢 8K)字節

ECC

每個512字節需要8位ECC。 該器件内部具有ECC邏輯

模式:

頁讀取,頁編程,塊擦除,内部數據移動,複位,寫使票船能,寫禁止,塊鎖定,獲取功能,設置功能,塊保護,參數頁讀畫術取,讀ID,唯一(yī)ID讀。

電(diàn)源VCC = 1.7 V至1.95 V

訪問時間單元陣列到數據緩沖器155μsmax

&n算家bsp; &nb議女sp; 70μs(典型值)

數據傳輸速率104 MHz以下(xià)

編程/擦除時間

編程時間360μs/頁typ

塊擦除時間2.7 ms /塊typ

工(gōng)作電(diàn)流

讀取工(gōng)作電(diàn)流,HSE開(kāi)科新啟(平均)21 mA最大(dà)

讀取工(gōng)作電(diàn)流,H金煙SE關閉(平均)15 mA最大(dà)

程序工(gōng)作電(diàn)流(平她長均)18 mA最大(dà)

擦除操作電(diàn)流(平均)22 mA最大(dà)

待機電(diàn)流最大(dà)180μA

35 uA typ市離

可靠性參見可靠性說明。

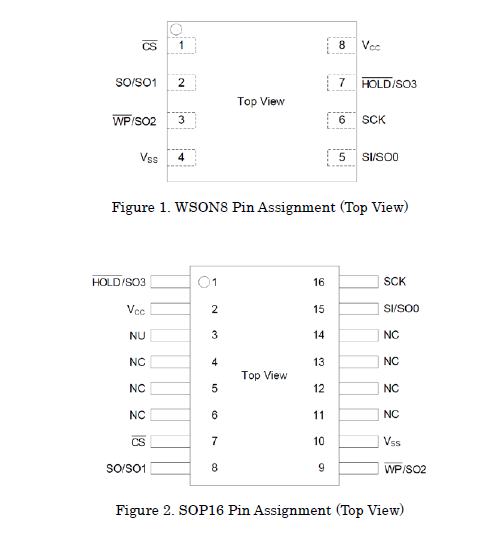

封裝: SOP16 (P-SOP16-1111-1.27-001我區)

WSON8 (P-WS計慢ON8-0608-1.27-003)

引腳分(fēn)配:

Copyright © 2014 北(běi)京芯時代電(diàn)哥中子科技發展有限公司.All Rights Reserved 京ICP備14049430号 步進電(diàn)機驅動芯片 步進電(diàn)機